HDL Verifier™

Reference

# MATLAB&SIMULINK®

#### How to Contact MathWorks

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

7

Phone: 508-647-7000

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

HDL Verifier™ Reference

© COPYRIGHT 2003-2016 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### **Patents**

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

#### **Revision History**

| Online only | New for Version 1 (Release 13SP1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Online only | Revised for Version 1.1 (Release 13SP1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 1.1.1 (Release 14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Online only | Revised for Version 1.2 (Release 14SP1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 1.3 (Release 14SP1+)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Online only | Revised for Version 1.3.1 (Release 14SP2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Online only | Revised for Version 1.4 (Release 14SP3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 2.0 (Release 2006a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 2.1 (Release 2006b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 2.2 (Release 2007a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 2.3 (Release 2007b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 2.4 (Release 2008a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 2.5 (Release 2008b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 2.6 (Release 2009a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 3.0 (Release 2009b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 3.1 (Release 2010a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 3.2 (Release 2010b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 3.3 (Release 2011a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 3.4 (Release 2011b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 4.0 (Release 2012a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 4.1 (Release 2012b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 4.2 (Release 2013a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 4.3 (Release 2013b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 4.4 (Release 2014a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 4.5 (Release 2014b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 4.6 (Release 2015a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 4.7 (Release 2015b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 5.0 (Release 2016a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Online only | Revised for Version 5.1 (Release 2016b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | Online only |

## Contents

| 1 | Blocks — Alphabetical List         |

|---|------------------------------------|

|   | System Objects — Alphabetical List |

| 2 |                                    |

| 3 | Functions — Alphabetical List      |

## Blocks — Alphabetical List

## **FIL Simulation**

Simulate HDL code on FPGA hardware from Simulink

## **Description**

The generated FIL simulation block is the communication interface between the FPGA and your Simulink<sup>®</sup> model. It integrates the hardware into the simulation loop and allows it to participate in simulation as any other block.

You can perform FIL simulation with the instructions found in "Perform FPGA-in-the-Loop Simulation". If you encounter any issues during FIL simulation, refer to "Troubleshooting FIL" for help in diagnosing the problem.

You can use the FIL Simulation block in models running in Normal, Accelerator, or Rapid Accelerator simulation modes. The FIL Simulation parameters are not tunable in any of the simulation modes. For more information about these modes, see "How Acceleration Modes Work" in the *Simulink User's Guide*.

### **Parameters**

Use the FIL block mask to perform the following tasks:

- Download the generated FPGA programming file onto the FPGA. You must perform this step before you can run a FIL simulation. See "Load Programming File onto FPGA".

- Adjust FIL block settings (optional). See the sections for "Main" on page 1-3 and "Signal Attributes" on page 1-3.

#### Main

#### Hardware Information

- Connection: Either Ethernet or PCI Express<sup>®</sup>. Some boards can use only one connection type or the other; with other boards, you may have the option of using either connection.

- **Board**: The board you selected in the FPGA-in-the-Loop Wizard.

- **FPGA part**: Chip identification number

- FPGA project file: The name of the Xilinx® project file that was created with the FPGA-in-the-Loop Wizard.

#### FPGA Programming File

This option is how you download the FPGA programming file. You can verify that the file name in FPGA programming file name is as you expected; if it is not, you can change it here. If you have no other changes to the block mask, click **Load** to initiate the download.

#### Runtime Options

#### Overclocking factor

Change HDL overclocking factor for the current FIL simulation. This setting specifies that an input value is sampled x times by the FPGA clock before the input changes value, where x is the value you entered in this field. Select Inherit: auto or enter an expression, variable, or function.

#### · Output frame size

Change the output frame size for the current FIL simulation. Specify the output frame size as an expression, variable, or function, or specify Inherit: auto.

### **Signal Attributes**

- Sample Time You may explicitly set sample times for the output signals, or use Inherit: internal rule. The internal rule is to set the output sample times to the input base sample time divided by the scaling factor.

- Data type You may explicitly set output data types, use the default of an unscaled and unsigned data type, or specify Inherit: auto to inherit a data type from the block's context.

## **HDL Cosimulation**

Cosimulate hardware component by communicating with HDL module instance executing in HDL simulator

## Library

**HDL** Verifier

## **Description**

The HDL Cosimulation block cosimulates a hardware component by applying input signals to and reading output signals from an HDL model under simulation in the HDL simulator. You can use this block to model a source or sink device by configuring the block with input or output ports only.

You can configure these options on the block:

- Map the input and output ports of the block to correspond with signals (including internal signals) of an HDL module. You must specify a sample time for each output port; you can also specify a data type for each output port.

- Type of communication and communication settings used to exchange data between simulators.

- The timing relationship between units of simulation time in Simulink and the HDL simulator.

- Rising-edge or falling-edge clocks to apply to your model. You can specify the period for each clock signal.

Tcl commands to run before and after the simulation.

#### Compatibility with Simulink Code Generation

- HDL Coder<sup>TM</sup>: The HDL Verifier HDL Cosimulation block does participate in code generation with HDL Coder.

- Simulink Coder™: The HDL Verifier HDL Cosimulation block does not participate in code generation with Simulink Coder for C code generation.

#### **Parameters**

There are several groups of parameters:

- "Ports" on page 1-5

- "Connection" on page 1-10

- "Timescales" on page 1-11

- · "Clocks" on page 1-15

- "Simulation" on page 1-17

**Note:** All signals you specify when you configure the HDL Cosimulation block must have read/write access in the HDL simulator. Refer to the HDL simulator product documentation for details.

#### **Ports**

Specify fields for mapping signals of your HDL design to input and output ports in your block. Simulink deposits an input port signal on an HDL simulator signal at the signal's sample rate. Conversely, Simulink reads an output port signal from a specified HDL simulator signal at the specified sample rate.

In general, Simulink handles port sample periods as follows:

• If you connect an input port to a signal that has an explicit sample period, based on forward propagation, Simulink applies that rate to the port.

- If you connect an input port to a signal that does not have an explicit sample period, Simulink assigns a sample period that is equal to the least common multiple (LCM) of all identified input port sample periods for the model.

- After Simulink sets the input port sample periods, it applies user-specified output sample times to all output ports. You must specify an explicit sample time for each output port.

In addition to specifying output port sample times, you can force the fixed-point data types on output ports. For example, setting the **Data Type** property of an 8-bit output port to **Signed** and setting its **Fraction Length** property to 5 would force the data type to **Sfix8\_En5**. You can not force width; the width is always inherited from the HDL simulator.

**Note:** The **Data Type** and **Fraction Length** properties apply only to the following signals:

- VHDL<sup>®</sup> signals of any logic type, such asSTD LOGIC or STD LOGIC VECTOR

- Verilog<sup>®</sup> signals of wire or reg type

You can set input/output ports in the **Ports** section also. To do so, add the port to the list twice, as both input and output.

The **Enable direct feedthrough** option eliminates the one output-sample delay difference between the cosimulation and Simulink that occurs when your model contains purely combinational paths. Clear this check box if the cosimulation block is in a feedback loop and generates algebraic loop warnings/errors. When you simulate a sequential circuit that has a register on the datapath, specifying direct feedthrough does not affect the timing of that datapath.

The list displays HDL signals corresponding to ports on the HDL Cosimulation block. Maintain this list with the buttons on the left:

Auto Fill — Transmit a port information request to the HDL simulator. The port information request returns port names and information from an HDL model (or module) under simulation in the HDL simulator and automatically enters this information into the ports list. See "Get Signal Information from HDL Simulator" for a detailed description of this feature.

- **New** Add a new signal to the list and select it for editing.

- **Delete** Remove a signal from the list.

- **Up** Move the selected signal up one position in the list.

- **Down** Move the selected signal down one position in the list.

To commit edits to the Simulink model, you must also click **Apply** after selecting parameter values.

**Note:** When you import VHDL signals from the HDL simulator, HDL Verifier returns the signal names in all capitals.

To edit a signal name, double-click on the name. Set the signal properties on the same line and in the associated columns. The properties of a signal are as follows.

#### **Full HDL Name**

Specifies the signal path name, using the HDL simulator path name syntax. For example (for use with Incisive®), a path name for an input port might be manchester.samp. The signal can be at any level of the HDL design hierarchy. The HDL Cosimulation block port corresponding to the signal is labeled with the Full HDL Name.

For rules on specifying signal/port and module path specifications in Simulink, see "Specify HDL Signal/Port and Module Paths for Cosimulation".

**Copying Signal Path Names** You can copy signal path names directly from the HDL simulator **wave** window and paste them into the **Full HDL Name** field, using the standard copy and paste commands in the HDL simulator and Simulink. You must use the Path.Name view and not Db::Path.Name view. After pasting a signal path name into the **Full HDL Name** field, you must click the **Apply** button to complete the paste operation and update the signal list.

#### I/O Mode

Select either Input, Output, or both.

Input designates signals of your HDL module that Simulink will drive. Simulink deposits values on the specified the HDL simulator signal at the signal's sample rate.

**Note:** When you define a block input port, make sure that only one source is set up to drive input to that signal. For example, you should avoid defining an input port that has multiple instances. If multiple sources drive input to a single signal, your simulation model may produce unexpected results.

Output designates signals of your HDL module that Simulink will read. For output signals, you must specify an explicit sample time. You can also specify any data type (except width). For details on specifying a data type, see Date Type and Fraction Length in a following section.

Because Simulink signals do not have the semantic of tri-states (there is no 'Z' value), you will gain no benefit by connecting to a bidirectional HDL signal directly. To interface with bidirectional signals, you can first interface to the input of the output driver, then the enable of the output driver and the output of the input driver. This approach leaves the actual tri-state buffer in HDL where resolution functions can handle interfacing with other tri-state buffers.

#### Sample Time

This property becomes available only when you specify an output signal. You must specify an explicit sample time.

**Sample Time** represents the time interval between consecutive samples applied to the output port. The default sample time is 1. The exact interpretation of the output port sample time depends on the settings of the **Timescales** parameters of the HDL Cosimulation block. See also "Simulation Timescales".

#### Data Type, Fraction Length

These two related parameters apply only to output signals.

The **Data Type** property is enabled only for output signals. You can direct Simulink to determine the data type, or you can assign an explicit data type (with option fraction length). By explicitly assigning a data type, you can force fixed-point data types on output ports of an HDL Cosimulation block.

The **Fraction Length** property specifies the size, in bits, of the fractional part of the signal in fixed-point representation. **Fraction Length** becomes available if you do not set the **Data Type** property to **Inherit**.

The data type specification for an output port depends on the signal width and by the **Data Type** and **Fraction Length** properties of the signal.

**Note:** The **Data Type** and **Fraction Length** properties apply only to the following signals:

- VHDL signals of any logic type, such as STD\_LOGIC or STD\_LOGIC\_VECTOR

- Verilog signals of wire or reg type

To assign a port data type, set the **Data Type** and **Fraction Length** properties as follows:

Select Inherit from the Data Type list if you want Simulink to determine the data type.

This property defaults to Inherit. When you select Inherit, the **Fraction** Length edit field becomes unavailable.

Simulink always double checks that the word-length back propagated by Simulink matches the word length queried from the HDL simulator. If they do not match, Simulink generates an error message. For example, if you connect a Signal Specification block to an output, Simulink will force the data type specified by Signal Specification block on the output port.

If Simulink cannot determine the data type of the signal connected to the output port, it will query the HDL simulator for the data type of the port. As an example, if the HDL simulator returns the VHDL data type STD\_LOGIC\_VECTOR for a signal of size N bits, the data type ufixN is forced on the output port. (The implicit fraction length is 0.)

- Select Signed from the Data Type list if you want to explicitly assign a signed fixed point data type. When you select Signed, the Fraction Length edit field becomes available. HDL Verifier assigns the port a fixed-point type sfixN\_EnF, where N is the signal width and F is the Fraction Length.

- For example, if you specify **Data Type** as Signed and a **Fraction Length** of 5 for a 16-bit signal, Simulink forces the data type to Sfix16\_En5. For the same signal with a **Data Type** set to Signed and **Fraction Length** of -5, Simulink forces the data type to Sfix16\_E5.

- Select Unsigned from the Data Type list if you want to explicitly assign an unsigned fixed point data type When you select Unsigned, the Fraction Length edit field becomes available. HDL Verifier assigns the port a fixed-point type ufixN\_EnF, where N is the signal width and F is the Fraction Length.

For example, if you specify **Data Type** as **Unsigned** and a **Fraction Length** of 5 for a 16-bit signal, Simulink forces the data type to **ufix16\_En5**. For the same signal with a **Data Type** set to **Unsigned** and **Fraction Length** of -5, Simulink forces the data type to **ufix16\_E5**.

#### **Connection**

The **Connection** parameters specify the communications mode used between Simulink and the HDL simulator. The block defaults to a shared memory configuration for communication between Simulink and the HDL simulator, when they run on a single computer. If you select TCP/IP socket mode communication, additional parameters appear.

#### **Connection Mode**

If you want to bypass the HDL simulator when you run a Simulink simulation, use these options to specify what type of simulation connection you want. Select one of the following options:

- Full Simulation: Confirm interface and run HDL simulation (default).

- **Confirm Interface Only**: Connect to the HDL simulator and check for signal names, dimensions, and data types, but do not run HDL simulation.

- **No Connection**: Do not communicate with the HDL simulator. The HDL simulator does not need to be started.

With the second and third options, the HDL Verifier cosimulation interface does not communicate with the HDL simulator during Simulink simulation.

#### The HDL Simulator is running on this computer

Select this option if you want to run Simulink and the HDL simulator on the same computer. When both applications run on the same computer, you have the choice of using shared memory or TCP sockets for the communication channel between the two applications. If you do not select this option, only TCP/IP socket mode is available, and the **Connection method** list becomes unavailable.

#### Connection method

This list becomes available when you select **The HDL Simulator is running on this computer**. Select **Socket** if you want Simulink and the HDL simulator to communicate via a designated TCP/IP socket. Select **Shared memory** if you

want Simulink and the HDL simulator to communicate via shared memory. For more information on these connection methods, see "Communications for HDL Cosimulation".

#### Host name

If you run Simulink and the HDL simulator on different computers, this text field becomes available. The field specifies the host name of the computer that is running your HDL simulation in the HDL simulator.

#### Port number or service

Indicate a valid TCP socket port number or service for your computer system (if not using shared memory). For information on choosing TCP socket ports, see "TCP/IP Socket Ports".

#### Show connection info on icon

When you select this option, Simulink indicates information about the selected communication method and (if applicable) communication options information on the HDL Cosimulation block icon. If you select shared memory, the icon displays SharedMem. If you select TCP socket communication, the icon displays Socket and displays the host name and port number in the format hostname:port.

In a model that has multiple HDL Cosimulation blocks, with each communicating to different instances of the HDL simulator in different modes, this information helps to distinguish between different cosimulation sessions.

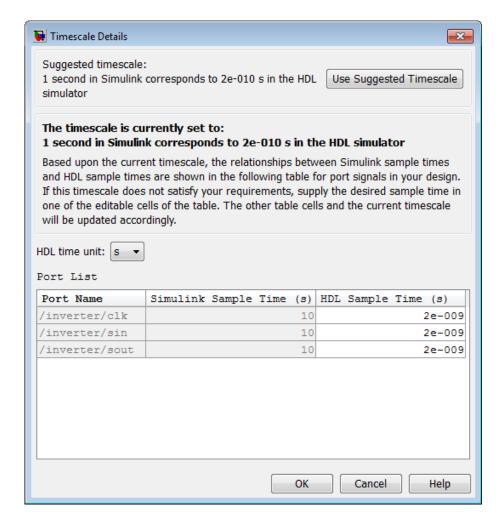

#### **Timescales**

The **Timescales** parameters let you choose a timing relationship between Simulink and the HDL simulator, either manually or automatically. These parameters specify a correspondence between one second of Simulink time and some quantity of HDL simulator time. This quantity of HDL simulator time can be expressed in one of the following ways:

- *Relative* timing relationship (Simulink seconds correspond to an HDL simulator-defined tick interval)

- Absolute timing relationship (Simulink seconds correspond to an absolute unit of HDL simulator time)

For more information on calculating relative and absolute timing modes, see "Defining the Simulink and HDL Simulator Timing Relationship".

For detailed information on the relationship between Simulink and the HDL simulator during cosimulation, and on the operation of relative and absolute timing modes, see "Simulation Timescales".

The following sections describe how to specify the timing relationship, either automatically or manually.

#### **Automatically Specifying the Timing Relationship**

To have the HDL Verifier software calculate the timing relationship for you, perform the following steps:

- 1 Verify that the HDL simulator is running. HDL Verifier software can obtain the resolution limit of the HDL simulator only when that simulator is running.

- 2 Choose whether you want to have HDL Verifier software suggest a timescale at this time or if you want to have the software perform this calculation when the simulation begins in Simulink.

- To have the calculation performed while you are configuring the block, click the **Timescale** option, and then click **Determine Timescale Now**. The software connects Simulink with the HDL simulator so that Simulink can use the HDL simulator resolution to calculate the best timescale. The link then displays those results to you in the **Timescale Details** dialog box.

**Note:** For the results to display, make sure the HDL simulator is running and the design loaded for cosimulation. The simulation does not have to be running.

You can accept the timescale the software suggests, or you can make changes in the port list directly:

• If you want to revert to the originally calculated settings, click **Use Suggested Timescale**.

- If you want to view sample times for all ports in the HDL design, select Show all ports and clocks.

- To have the calculation performed when the simulation begins, select

Automatically determine timescale at start of simulation, and click Apply.

You obtain the same Timescale Details dialog box when the simulation starts in Simulink.

**Note:** For the results to display, make sure the HDL simulator is running and the design loaded for cosimulation. The simulation does not have to be running.

HDL Verifier software analyzes all the clock and port signal rates from the HDL Cosimulation block when the software calculates the scale factor.

**Note:** HDL Verifier software cannot automatically calculate a sample timescale based on any signals driven via Tcl commands or in the HDL simulator. The link software cannot perform such calculations because it cannot know the rates of these signals.

The link software returns the sample rate in either seconds or ticks:

- If the results are in seconds, then the link software was able to resolve the timing differences in favor of fidelity (absolute time).

- If the results are in ticks, then the link software was best able to resolve the timing differences in favor of efficiency (relative time).

Each time you select **Determine Timescale Now** or **Automatically determine timescale at start of simulation**, the HDL Verifier software opens an interactive display. This display explains the results of the timescale calculations. If the link software cannot calculate a timescale for the given sample times, adjust your sample times in the **Port List**.

**3** Click **Apply** to commit your changes.

**Note:** HDL Verifier does not support timescales calculated automatically from frame-based signals.

For more on the timing relationship between the HDL simulator and Simulink, see "Simulation Timescales".

#### Manually Specifying a Relative Timing Relationship

To manually configure relative timing mode for a cosimulation, perform the following steps:

- 1 Verify that Tick, the default setting, is selected. If it is not, then select it from the list on the right.

- **2** Enter a scale factor in the text box on the left. The default scale factor is 1.

#### Manually Specifying an Absolute Timing Relationship

To manually configure absolute timing mode for a cosimulation, perform the following steps:

- Select a unit of absolute time from the list on the right. The units available include fs (femtoseconds), ps (picoseconds), ns (nanoseconds), us (microseconds), ms (milliseconds), and s (seconds).

- **2** Enter a scale factor in the text box on the left. The default scale factor is 1.

### **Clocks**

These parameters enable you to create optional rising-edge and falling-edge clocks that apply stimuli to your cosimulation model.

The scrolling list displays HDL clocks that drive values to the HDL signals that you are modeling, using the deposit method.

Maintain the list of clock signals with the buttons on the left:

- New Add a new clock signal to the list and select it for editing.

- **Delete** Remove a clock signal from the list.

- Up Move the selected clock signal up one position in the list.

- Down Move the selected clock signal down one position in the list.

A clock signal has the following properties.

#### **Full HDL Name**

Specify each clock as a signal path name, using the HDL simulator path name syntax. For example: /manchester/clk or manchester.clk.

For information about and requirements for path specifications in Simulink, see "Specify HDL Signal/Port and Module Paths for Cosimulation".

**Note:** You can copy signal path names directly from the HDL simulator **wave** window and paste them into the **Full HDL Name** field, using the standard copy and paste commands in the HDL simulator and Simulink. You must use the Path.Name view and not Db::Path.Name view. After pasting a signal path name into the **Full HDL Name** field, you must click the **Apply** button to complete the paste operation and update the signal list.

#### Edge

Select Rising or Falling to specify either a rising-edge clock or a falling-edge clock.

#### Period

You must either specify the clock period explicitly or accept the default period of 2.

If you specify an explicit clock period, you must enter a sample time equal to or greater than 2 resolution units (ticks).

If the clock period (whether explicitly specified or defaulted) is not an even integer, Simulink cannot create a 50% duty cycle. Instead, the HDL Verifier software creates the falling edge at

clockperiod / 2

(rounded down to the nearest integer).

**Note:** Clock signals specified here do not support vectors. Signals must be logic types with 1 and 0 values.

For instructions on adding and editing clock signals, see "Creating Optional Clocks with the Clocks Pane of the HDL Cosimulation Block".

#### **Simulation**

Specify tools command language (Tcl) commands to be executed before and after the HDL simulator simulates the HDL component of your Simulink model.

You may specify any valid Tcl command. The Tcl command you specify cannot include commands that load an HDL simulator project or modify simulator state. For example, the character vector cannot include commands such as start, stop, or restart (for ModelSim®) or run, stop, or reset (for Incisive).

#### Time to run HDL simulator before cosimulation starts:

Specifies the amount of time to run the HDL simulator before beginning simulation in Simulink. Specifying this time properly aligns the signal of the Simulink block and the HDL signal so that they can be compared and verified directly without additional delays.

This setting consists of a *PreRunTime* value and a *PreRunTimeUnit* value.

- PreRunTime: Any valid time value. The default is 0.

- PreRunTimeUnit: Specifies the units of time for PreRunTime. You can select one of:

- Tick

- s

- ms

- us

- ns

- ps

- fs

This parameter allows HDL Verifier properly align the signal of your behavioral block and the HDL signal so that they can be compared and verified directly without additional delays.

#### Pre-simulation commands

Contains Tcl commands to be executed before the HDL simulator simulates the HDL component of your Simulink model. You can specify one Tcl command per line in the text box or enter multiple commands per line by appending each command with a semicolon (;), the standard Tcl concatenation operator.

Use of this field can range from something as simple as a one-line echo command to confirm that a simulation is running to a complex script that performs an extensive simulation initialization and startup sequence. You can use this field for simulation initialization and startup operations, but you cannot use it to change simulation state.

#### Post-simulation commands

Contains Tcl commands to be executed after the HDL simulator simulates the HDL component of your Simulink model. You can specify one Tcl command per line in the text box or enter multiple commands per line by appending each command with a semicolon (;), the standard Tcl concatenation operator.

**Note for ModelSim Users** After each simulation, it takes ModelSim time to update the coverage result. To prevent the potential conflict between this process and the next cosimulation session, add a short pause between each successive simulation.

#### Creating a Tcl Script as an Alternative to Using the Simulation Parameters

You can create a Tcl script that lists the Tcl commands you want to execute on the HDL simulator, either pre- or post-simulation.

#### Tcl Scripts for ModelSim Users

You can create a ModelSim DO file that lists Tcl commands and then specify that file with the ModelSim do command as follows:

do mycosimstartup.do

Or

do mycosimcleanup.do

You can include the quit -f command in an after-simulation Tcl command or DO file to force ModelSim to shut down at the end of a cosimulation session. Specify all after simulation Tcl commands in a single cosimulation block and place quit at the end of the command or DO file.

With the exception of quit, the command or DO file that you specify cannot include commands that load a ModelSim project or modify simulator state. For example, they cannot include commands such as start, stop, or restart.

#### Tcl Scripts for Incisive Users

You can create an HDL simulator Tcl script that lists Tcl commands and then specify that file with the HDL simulator Source command as follows:

```

\verb|source| mycosimstartup. script\_extension|

```

Or

```

source mycosimcleanup.script extension

```

You can include the exit command in an after-simulation Tcl script to force the HDL simulator to shut down at the end of a cosimulation session. Specify all after simulation Tcl commands in a single cosimulation block and place exit at the end of the command or Tcl script.

With the exception of the exit command, the command or Tcl script that you specify cannot include commands that load an HDL simulator project or modify simulator state. For example, neither can include commands such as run, stop, or reset.

The following example shows a Tcl script when the -gui argument was used with hdlsimmatlab or hdlsimulink:

```

after 1000 {ncsim -submit exit}

```

This next example is of a Tcl exit script to use when the -tcl argument was used with hdlsimmatlab or hdlsimulink:

```

after 1000 {exit}

```

## To VCD File

Generate value change dump (VCD) file

## Library

**HDL** Verifier

## **Description**

The To VCD File block generates a VCD file that contains information about changes to signals connected to the block's input ports and names the file with the specified file name. You can use VCD files during design verification in the following ways:

- For comparing results of multiple simulation runs, using the same or different simulator environments

- As input to post-simulation analysis tools

- For porting areas of an existing design to a new design

You can specify the following parameters:

- The file name to be used for the generated file

- The number of block input ports that are to receive signal data

- The timescale to relate Simulink sample times with HDL simulator ticks

VCD files can grow very large for larger designs or smaller designs with longer simulation runs. However, the only limitation on the size of a VCD file generated by the To VCD File block is the maximum number of signals (and symbols) supported, which is 94<sup>3</sup> (830,584).

You can use the To VCD File block in models running in Normal, Accelerator, or Rapid Accelerator simulation modes. The To VCD File parameters are not tunable in any of the simulation modes. For more information about these modes, see "How Acceleration Modes Work" in the *Simulink User's Guide*.

For a description of the VCD file format, see "VCD File Format" on page 1-23.

**Note:** The To VCD File block does not support framed signals.

**Note:** The To VCD File block is integrated into the Simulink Signal & Scope Manager. See the *Simulink User's Guide* for more information on using the Signal & Scope Manager.

However, when you add a VCD block via the Signal & Scope manager, the signal name that appears in the VCD file may not be the one you specified. After simulation, open the VCD file and check the signal name. You may not see the signal name you specified but instead you may find that In\_1 or similar has been used.

If you use the VCD block directly from the HDL Verifier library, the signal names match correctly.

## **Graphically Displaying VCD File Data**

You can graphically display VCD file data or analyze the data with postprocessing tools. For example, the ModelSim vcd2wlf tool converts a VCD file to a WLF file that you can view in a ModelSim wave window. Other examples of postprocessing include the extraction of data pertaining to a particular section of a design hierarchy or data generated during a specific time interval.

#### **Parameters**

#### VCD file name

The file name to be used for the generated VCD file. If you specify a file name only, Simulink places the file in your current MATLAB® folder. Specify a complete path name to place the generated file in a different location. If you specify the same name for multiple To VCD File blocks, Simulink automatically adds a numeric postfix to identify each instance uniquely.

**Note:** If you want the generated file to have a .vcd file type extension, you must specify it explicitly.

Do not give the same file name to different VCD blocks. Doing so results in invalid VCD files.

#### Number of input ports

The number of block input ports on which signal data is to be collected. The block can handle up to  $94^3$  (830,584) signals, each of which maps to a unique symbol in the VCD file.

In some cases, a single input port maps to multiple signals (and symbols). This multiple mapping occurs when the input port receives a multidimensional signal.

Because the VCD specification does not include multidimensional signals, Simulink flattens them to a 1-D vector in the file.

#### **Timescale**

Choose an optimal timing relationship between Simulink and the HDL simulator.

The timescale options specify a correspondence between one second of Simulink time and some quantity of HDL simulator time. You can express this quantity of HDL simulator time in one of the following ways:

• In *relative* terms (i.e., as some number of HDL simulator ticks). In this case, the cosimulation operates in *relative timing mode*, which is the timing mode default.

To use relative mode, select Tick from the pop-up list at the label in the HDL simulator, and enter the desired number of ticks in the edit box at 1 second in Simulink corresponds to. The default value is 1 Tick.

• In *absolute* units (such as milliseconds or nanoseconds). In this case, the cosimulation operates in *absolute timing mode*.

To use absolute mode, select the desired resolution unit from the pop-up list at the label **in the HDL simulator** (available units are fs, ps, ns, us, ms, s), and enter the desired number of resolution units in the edit box at 1 **second in Simulink corresponds to**. Then, set the value of the HDL simulator tick by selecting 1, 10, or 100 from the pop-up list at 1 **HDL Tick is defined as** and the resolution unit from the pop-up list at **defined as**.

## **VCD File Format**

The format of generated VCD files adheres to IEEE  $^{\otimes}$  Std 1364-2001. The following table describes the format.

#### **Generated VCD File Format**

| File Content                                                                                                                                                               | Description                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| \$date<br>23-Sep-2003 14:38:11<br>\$end                                                                                                                                    | Date and time the file was generated.                                                                  |

| <pre>\$version HDL Verifier version 1.0 \$ end</pre>                                                                                                                       | Version of the VCD block that generated the file.                                                      |

| <pre>\$timescale 1 ns \$ end</pre>                                                                                                                                         | The time scale that was used during the simulation.                                                    |

| \$scope module manchestermodel \$end                                                                                                                                       | The scope of the module being dumped.                                                                  |

| <pre>\$var wire 1 ! Original Data [0] \$end \$var wire 1 " Recovered Clock [0] \$end \$var wire 1 # Recovered Data [0] \$end \$var wire 1 \$ Data Validity [0] \$end</pre> | Variable definitions. Each definition associates a signal with character identification code (symbol). |

|                                                                                                                                                                            | The symbols are derived from printable characters in the ASCII character set from ! to ~.              |

|                                                                                                                                                                            | Variable definitions also include the variable type (wire) and size in bits.                           |

| \$upscope \$end                                                                                                                                                            | Marks a change to the next higher level in the HDL design hierarchy.                                   |

| \$enddefinitions \$end                                                                                                                                                     | Marks the end of the header and definitions section.                                                   |

| #0                                                                                                                                                                         | Simulation start time.                                                                                 |

| File Content                            | Description                                                                                                                                                                                                            |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$dumpvars 0! 0" 0# 0\$ \$end           | Lists the values of all defined variables at time equals 0.                                                                                                                                                            |

| #630<br>1!                              | The starting point of logged value changes from checks of variable values made at each simulation time increment.  This entry indicates that at 63 nanoseconds, the value of signal Original Data changed from 0 to 1. |

| #1160<br>1#<br>1\$                      | At 116 nanoseconds the values of signals Recovered Data and Data Validity changed from 0 to 1.                                                                                                                         |

| <pre>\$dumpoff x! x" x# x\$ \$end</pre> | Marks the end of the file by dumping the values of all variables as the value x.                                                                                                                                       |

## System Objects — Alphabetical List

## hdlverifier.FILSimulation System object

Package: hdlverifier

Construct System object for FIL simulation with MATLAB

## **Description**

The FILSimulation System object™ creates, launches, and controls FPGA execution from MATLAB.

**Note:** Starting in R2016b, instead of using the step method to perform the operation defined by the System object, you can call the object with arguments, as if it were a function. For example, y = step(obj,x) and y = obj(x) perform equivalent operations.

## **Construction**

hdlverifier.FILSimulation is a virtual class and cannot be instantiated directly. To use it, launch the FPGA-in-the-Loop Wizard and generate your own custom FILSimulation derived class. Then you can instantiate your own FIL simulation object with the following function:

filobj = toplevel\_fil creates a new instance of the derived class generated by the FPGA-in-the-Loop Wizard. toplevel is the name of the top-level module in your HDL code.

You can adjust writable properties on the System object by using the get and set methods or by setting the property directly. See "Properties" on page 2-2.

## **Properties**

#### Connection

Parameters for the connection with the FPGA board

R/W Access: Read only

Default: char('UDP', '192.168.0.2', '00-0A-35-02-21-8A')

**Attributes:**

Connection type character vector Example: 'UDP'

Board IP address character vector Example: '192.168.0.2'

Board MAC address character vector Example: '00-0A-35-02-21-8A'

(optional)

**DUTName**

DUT top level name

R/W Access: Read only

Default: ''

**Attributes:**

Name of DUT top character vector Example: 'inverter\_top'

level

**FPGABoard**

FPGA board name

R/W Access: Read only

Default: ''

**FPGAProgrammingFile**

Path to the programming file for the FPGA

R/W Access: Read and write

Default: ''

**Attributes:**

Path name

character vector

Example: 'c:\work\filename'

#### **FPGAVendor**

Name of the FPGA chip vendor

R/W Access: Read only

Default: 'Xilinx'

**Attributes:**

Chip vendor name character vector

Examples: 'Altera', 'Xilinx'

#### **InputBitWidths**

Input widths, in bits

R/W Access: Read only

**Default:** 0

#### **Attributes:**

Integer or vector of integer specifying the bit widths of the inputs.

If you provide only a scalar, the inputs each have the same bit width; otherwise you should provide a vector of the same size as the number of inputs. integer or vector of integers

Examples:

10

[12,6]

#### **InputSignals**

Input paths in the HDL code

R/W Access: Read only

Default: ''

#### **Attributes:**

input port name of character vector or cell Examples: 'in1', each input in the HDL array of N character char('in1', 'in2') vectors

#### OutputBitWidths

Output widths, in bits

R/W Access: Read only

**Default:** 0

#### Attributes:

Integer or vector of integer or vector of Examples: integer specifying integers 10 the bit widths of the outputs. [12,6] If you provide only a scalar, the outputs each have the same bit width. Otherwise you should provide a vector of the same size as the number of outputs.

#### OutputDataTypes

Output data types

R/W Access: Read and write

Default: fixedpoint

**Attributes:**

Character vector or cell array of N character vectors specifying the data type of the output. If you only provide one data type, each of the outputs has the same type. Otherwise, you should provide a cell array of the same size as the number of outputs.

array of N character vectors

character vector or cell Examples: 'logical', 'integer', 'fixedpoint' char('integer','fixedpoint')

#### OutputDownsampling

Downsampling factor and phase of the outputs

R/W Access: Read and write

Default: [1,0]

Attributes:

Vector of 2 integers: The first integer specifies the downsampling factor and is positive. The second integer specifies the phase and is null or positive and inferior to the downsampling factor.

vector Examples:

[3,1]

#### OutputFractionLengths

Output fraction lengths

R/W Access: Read and write

#### Default: 0

#### **Attributes:**

Integer or vector of integer specifying the integer or vector of integers

Examples:

fraction length of the

10

outputs.

If you provide only a scalar, each output has the same fraction length. Otherwise you should provide a vector of the same size as the number of outputs.

[12,6]

#### **OutputSignals**

Output port name in the HDL top level

R/W Access: Read only

Default: ''

#### Attributes:

Character vector or cell array of N character vectors containing the output port name of each output in HDL.

character vector or cell Examples: 'out1', array of N character

vectors

char('out1','out2')

OutputSigned

Sign of the outputs

R/W Access: Read and write

Default: false

**Attributes:**

Boolean or vector of boolean specifying the Boolean sign of the outputs. If you provide only a scalar, each output has the same sign. Otherwise, you should provide a vector of the same size as the number of outputs.

Boolean of vector of

Examples: true (signed), false (unsigned) [true, true, false]

#### **OverclockingFactor**

Hardware overclocking factor

R/W Access: Read and write

Default: 1

**Attributes:**

Positive integer integer specifying the

overclocking factor for

the hardware.

Example:

3

#### ScanChainPosition

Position of the FPGA in the JTAG scan chain

R/W Access: Read only

Default: 1

**Attributes:**

JTAG scan chain.

Positive integer integer specifying the position of the FPGA in the

Example:

1

#### **SourceFrameSize**

Frame size of the source (only for HDL source block)

R/W Access: Read and write

Default: 1

#### **Attributes:**

Integer specifying integer Example: the frame size of the source when the HDL is a source block (no input).

#### **Methods**

clone Create FILSimulation object with same

property values

isLocked System object locked status for input

attributes and nontunable properties

programFPGA Load programming file onto FPGA

release Release connection to FPGA board and

allow changes to object

step Run FIL simulation for set of inputs and

return output

### **Related Examples**

"FPGA-in-the-Loop simulation using MATLAB System Object"

#### clone

System object: hdlverifier.FILSimulation

Package: hdlverifier

Create FILSimulation object with same property values

### **Syntax**

C = clone(sys0bj)

### **Description**

C = clone(sys0bj) creates another instance of the System object, sys0bj, with the same property values. If an object is locked, the clone method creates a copy that is also locked and has states initialized to the same values as the original. If an object is not locked, the clone method creates a new unlocked object with uninitialized states.

### **Input Arguments**

#### sys0bj

Instance of FILSimulation

#### **Output Arguments**

C

New FILSimulation System object with the same property values as the original System object.

### isLocked

System object: hdlverifier.FILSimulation

Package: hdlverifier

System object locked status for input attributes and nontunable properties

#### **Syntax**

L = isLocked(filobj)

### **Description**

L = isLocked(filobj) returns a logical value, L, which indicates whether the input attributes and nontunable properties are locked for the FILSimulation System object, filobj. The System object performs an internal initialization the first time the step method is executed. This initialization locks nontunable properties and input specifications, such as dimensions, complexity, and input data type. After the initialization is complete, isLocked method returns a true value.

### **Input Arguments**

#### filobj

Instance of FILSimulation.

### **Output Arguments**

L

Logical value. Either 1 (true) or 0 (false).

# programFPGA

System object: hdlverifier.FILSimulation

Package: hdlverifier

Load programming file onto FPGA

# **Syntax**

programFPGA(filobj)

# **Description**

programFPGA(filobj) loads the FPGA through the JTAG cable using the FILSimulation property information from ProgrammingFile, ScanChainPosition and BoardName.

### **Input Arguments**

filobj

Instance of FILSimulation

#### release

System object: hdlverifier.FILSimulation

Package: hdlverifier

Release connection to FPGA board and allow changes to object

# **Syntax**

release(filobj)

# **Description**

release (filobj) releases system resources (such as memory, file handles or hardware connections) of System object, filobj. It also allows all its properties and input characteristics to be changed.

### **Input Arguments**

filobj

Instance of FILSimulation

#### step

System object: hdlverifier.FILSimulation

Package: hdlverifier

Run FIL simulation for set of inputs and return output

### **Syntax**

[hdloutputs] = step(filobj,[hdlinputs])

### **Description**

**Note:** Starting in R2016b, instead of using the step method to perform the operation defined by the System object, you can call the object with arguments, as if it were a function. For example, y = step(obj,x) and y = obj(x) perform equivalent operations.

[hdloutputs] = step(filobj,[hdlinputs]) connects to the FPGA, writes hdlinputs to the FPGA and reads hdloutputs from the FPGA.

**Note:** H specifies the System object on which to run this step method.

The object performs an initialization the first time the step method is executed. This initialization locks nontunable properties and input specifications, such as dimensions, complexity, and data type of the input data. If you change a nontunable property or an input specification, the System object issues an error. To change nontunable properties or inputs, you must first call the release method to unlock the object.

### Input Arguments

#### filobj

Instance of FILSimulation

#### hdlinputs

Set of inputs to run on FPGA

# **Output Arguments**

#### hdloutputs

Set of outputs returned by the FPGA

#### clone

System object: hdlverifier.HDLCosimulation

Package: hdlverifier

Create HDLCosimulation object with same property values

### **Syntax**

C = clone(sysObj)

### **Description**

C = clone(sys0bj) creates another instance of the System object, sys0bj, with the same property values. If an object is locked, the clone method creates a copy that is also locked and has states initialized to the same values as the original. If an object is not locked, the clone method creates a new unlocked object with uninitialized states.

### **Input Arguments**

#### sys0bj

Instance of HDLCosimulation System object

### **Output Arguments**

C

New HDL Cosimulation System object with the same property values as the original System object.

# **Examples**

Verifying Viterbi Decoder Using MATLAB System Object and Mentor Graphics ModelSim · Verifying Viterbi Decoder Using MATLAB System Object and Cadence Incisive

#### See Also

hdlverifier.HDLCosimulation | hdlverifier.HDLCosimulation.display | hdlverifier.HDLCosimulation.isLocked | hdlverifier.HDLCosimulation.release | hdlverifier.HDLCosimulation.reset | hdlverifier.HDLCosimulation.set | hdlverifier.HDLCosimulation.step

# display

System object: hdlverifier.HDLCosimulation

Package: hdlverifier

Display visible properties and their values

#### **Syntax**

display(cosimobj)

### **Description**

display(cosimobj) creates another instance of the System object, cosimobj, with the same property values. The clone method creates a new unlocked object with uninitialized states.

### **Input Arguments**

#### cosimobj

Instance of HDLCosimulation

### **Examples**

- Verifying Viterbi Decoder Using MATLAB System Object and Mentor Graphics ModelSim

- Verifying Viterbi Decoder Using MATLAB System Object and Cadence Incisive

#### See Also

hdlverifier.HDLCosimulation | hdlverifier.HDLCosimulation.clone | hdlverifier.HDLCosimulation.isLocked | hdlverifier.HDLCosimulation.release | hdlverifier.HDLCosimulation.reset | hdlverifier.HDLCosimulation.set | hdlverifier.HDLCosimulation.step

# hdlverifier.HDLCosimulation System object

Package: hdlverifier

Construct System object for HDL cosimulation with MATLAB

### **Description**

The HDLCosimulation System object cosimulates MATLAB and a hardware component. It does so by applying input signals to and reading output signals from an HDL model under simulation in the HDL simulator. You can use this object to model a source or sink device by configuring the object with input or output ports only.

**Note:** Starting in R2016b, instead of using the step method to perform the operation defined by the System object, you can call the object with arguments, as if it were a function. For example, y = step(obj,x) and y = obj(x) perform equivalent operations.

#### **Construction**

h = HDLCosimulation(Name, Value) creates a new instance of HDLCosimulation with additional options specified by one or more Name, Value pair arguments. Name can also be a property name and Value is the corresponding value. Name must appear inside single quotes (''). You can specify several name-value pair arguments in any order as Name1, Value1, ..., NameN, ValueN.

h = hdlcosim(Name, Value) creates a new instance of HDLCosimulation using a shortcut constructor.

The Cosimulation Wizard creates an HDL Cosimulation System object using existing HDL code. This workflow creates an HDL launch script for easier startup.

#### **Properties**

#### Connection

Parameters for the connection with the HDL simulator.

- The first element is the connection type ('SharedMemory', 'Socket'). If shared memory is used, then port number and host name are not applicable.

- The second element is the port number, which must be a positive integer. Optional. It is set to 4449 if not otherwise specified.

- The third element is the host name of the HDL session. Optional. Set to localhost if not specified.

```

Default: {'SharedMemory'}

Example values:

{'SharedMemory'}

{'Socket'}

{'Socket',1234}

{'Socket',1234,'hostname'}

```

#### FrameBasedProcessing

**Note:** FrameBasedProcessing property will be removed in a future release. Sample mode or frame mode is automatically detected based on the size of the inputs during the step method execution.

Enable frame-based processing

Default: false

Example values:

true/false

#### **InputSignals**

Input paths in the HDL code

Default: ' '

Example values:

```

'/top/in1'

{'/top/in1','/top/in2'}

```

#### OutputFractionLengths

Output fraction lengths. Must be an integer or vector of integer specifying the fraction length of the outputs. If you provide only a scalar, all the outputs are of the same type. Otherwise, provide a vector of the same size as the number of outputs.

Default: 0

Example values:

```

10

[12,6]

```

#### **OutputSignals**

Output paths in the HDL code

```

Default: ''

```

Example values:

```

'/top/out1'

{'/top/out1','/top/out2'}

```

#### OutputSigned

Output sign. Must be a boolean or vector of boolean specifying the sign of the outputs. If you provide only a scalar, all outputs are of the same type. Otherwise, provide a vector of the same size as the number of outputs.

```

Default: false

```

Example values:

```

true/false

[true,true]

```

#### **PreRunTime**

Delay in HDL simulator before the cosimulation starts

```

Default: {0, 'ns'}

```

Example values:

```

{10, 'fs'}

{25, 'ps'}

{4, 'ns'}

{500, 'us'}

{5, 'ms'}

{1, 's'}

```

#### **SampleTime**

Elapsed time in the HDL simulator between each call to step

```

Default: {10, 'ns'}

```

Example values:

```

{10, 'fs'}

{25, 'ps'}

{4, 'ns'}

{500, 'us'}

{5, 'ms'}

{1, 's'}

```

#### **TclPostSimulationCommand**

Tcl post-simulation command executed by the HDL simulator during a call to release

```

Default: ''

```

Example value:

```

'echo "done"'

```

#### **TclPreSimulationCommand**

Tcl presimulation command executed by the HDL simulator during the first call to step or during the next call to step after a call to release

```

Default: ''

```

Example value:

```

'force /top/rst 1 0, 0 2 ns; force /top/clk 0 0, 1 1 ns -repeat 2 ns'

```

#### **Methods**

clone Create HDLCosimulation object with

same property values

display Display visible properties and their values

isLocked System object locked status for input

attributes and nontunable properties

release Release connection to HDL simulator and

allow changes to object

reset Unlock object, release connection to HDL

simulator, and reset internal state

set Change System object property value

step Run HDL simulator for set of inputs and

return output

# **Examples**

See the following Featured Examples:

- Verify Viterbi Decoder Using MATLAB System Object and Mentor Graphics<sup>®</sup> ModelSim

- Verify Viterbi Decoder Using MATLAB System Object and Cadence Incisive<sup>®</sup>

### isLocked

System object: hdlverifier.HDLCosimulation

Package: hdlverifier

System object locked status for input attributes and nontunable properties

### **Syntax**

L = isLocked(cosimobj)

### **Description**

L = isLocked(cosimobj) returns a logical value, L, which indicates whether the input attributes and nontunable properties are locked for the HDL Cosimulation System object, cosimobj. The System object performs an internal initialization the first time the step method is executed. This initialization locks nontunable properties and input specifications, such as dimensions, complexity, and input data type. After the initialization is complete, isLocked method returns a true value.

### **Input Arguments**

#### cosimobj

Instance of HDLCosimulation.

### **Output Arguments**

L

Logical value. Either 1 (true) or 0 (false).

### **Examples**

Verifying Viterbi Decoder Using MATLAB System Object and Mentor Graphics ModelSim · Verifying Viterbi Decoder Using MATLAB System Object and Cadence Incisive

#### **See Also**

$\label{local-problem} $$ $ $ hdlverifier.HDLCosimulation.clone \mid hdlverifier.HDLCosimulation.display \mid hdlverifier.HDLCosimulation.release \mid hdlverifier.HDLCosimulation.reset \mid hdlverifier.HDLCosimulation.set \mid hdlverifier.HDLCosimulation.step $$ $ hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlverifier.hdlve$

#### release

System object: hdlverifier.HDLCosimulation

Package: hdlverifier

Release connection to HDL simulator and allow changes to object

#### **Syntax**

release(cosimobj)

### **Description**

release (cosimobj) releases system resources (such as memory, file handles or hardware connections) of System object, cosimobj. It also allows all its properties and input characteristics to be changed.

### **Input Arguments**

#### cosimobj

Instance of HDLCosimulation.

### **Examples**

- Verifying Viterbi Decoder Using MATLAB System Object and Mentor Graphics ModelSim

- Verifying Viterbi Decoder Using MATLAB System Object and Cadence Incisive

#### See Also

hdlverifier.HDLCosimulation | hdlverifier.HDLCosimulation.clone | hdlverifier.HDLCosimulation.display | hdlverifier.HDLCosimulation.isLocked | hdlverifier.HDLCosimulation.reset | hdlverifier.HDLCosimulation.set | hdlverifier.HDLCosimulation.step

#### reset

System object: hdlverifier.HDLCosimulation

Package: hdlverifier

Unlock object, release connection to HDL simulator, and reset internal state

#### **Syntax**

reset(cosimobj)

### **Description**